| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

افزایش ایمنی الکترومغناطیسی پیشرفته مدارهای زیرآستانه با طراحی گیت های منطقی اشمیت تریگر منطقی با DTMOS |

| عنوان انگلیسی مقاله: |

Design of Schmitt Trigger Logic Gates Using DTMOS for Enhanced Electromagnetic Immunity of Subthreshold Circuits |

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار | 2015 |

| تعداد صفحات مقاله انگلیسی | 10صفحه با فرمت pdf |

| رشته های مرتبط با این مقاله | مهندسی برق |

| گرایش های مرتبط با این مقاله | مدارهای مجتمع الکترونیک، مهندسی الکترونیک، سیستم های قدرت و بیوالکتریک |

| مجله |

یافته ها در حوزه سازگاری الکترومغناطیس TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY |

| دانشگاه | کالج اطلاعات و ارتباطات مهندسی، دانشگاه Sungkyunkwan، سوئون، کره جنوبی |

| کلمات کلیدی | مدارهای دیجیتال، تداخل الکترومغناطیسی (EMI)، هیسترزیس، ایمنی، اشمیت تریگر |

| شناسه شاپا یا ISSN | ISSN 1558-187X |

| رفرنس | دارد |

| لینک مقاله در سایت مرجع | لینک این مقاله در سایت IEEE |

| نشریه آی تریپل ای | |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش و فونت 14 B Nazanin | 24صفحه |

| ترجمه عناوین تصاویر و جداول | ترجمه شده است |

| ترجمه متون داخل تصاویر | ترجمه نشده است |

| ترجمه متون داخل جداول | ترجمه نشده است |

| درج تصاویر در فایل ترجمه | درج شده است |

| درج جداول در فایل ترجمه | درج شده است |

| درج فرمولها و محاسبات در فایل ترجمه به صورت عکس | درج شده است |

| منابع داخل متن | درج نشده است |

- فهرست مطالب:

1. مقدمه

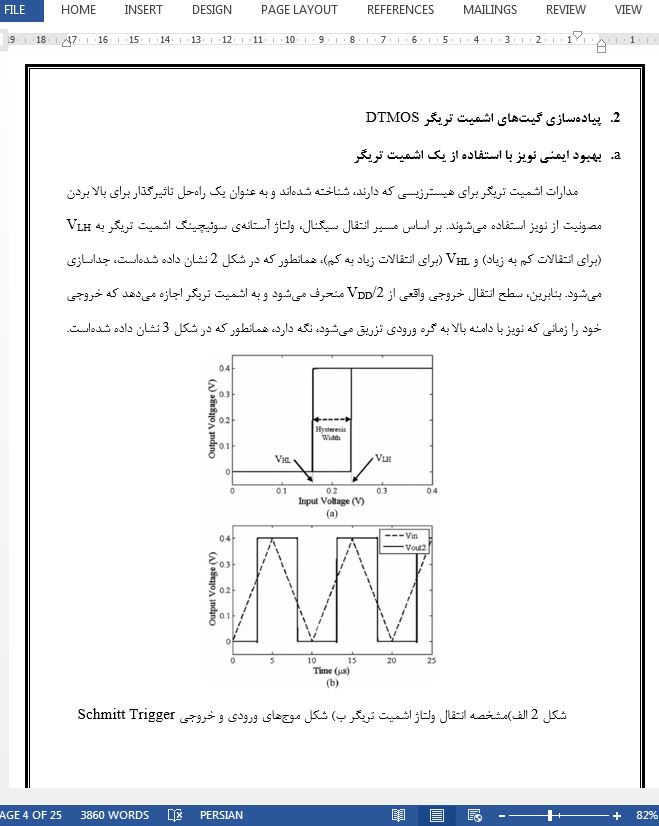

2. پیادهسازی گیتهای اشمیت تریگر DTMOS

a. بهبود ایمنی نویز با استفاده از یک اشمیت تریگر

b. ساختمان گیت AND و OR

3. بهبود مصونیت از نویز گیتهای اشمیت تریگر DTMOS

a. مقدمات شبیهسازی

b. افزایش ایمنی سطح گیت

c. بهبود ایمنی سطح مدار

4. اشمیتتریگر با هیسترزیس قابل تنظیم کامل

A. محدودیتهای طرح پیشنهادی

B. اشمیتتریگر با هیسترزیس قابل تنظیم کامل

5. بهبود گیتهای اشمیتتریگر DTMOS

A.. مقدمات شبیهسازی

B. ایمنی نویز (پهنای هیسترزیس)

C. توان مصرفی

D. تاخیر I/O

E. استخراج پهنای هیسترزیس بهینه

F. کاربرد IPDR در مدارهای پایه

6. نتیجهگیری

- بخشی از ترجمه:

6. نتیجهگیری

وقتی که ولتاژ منبع مدار کاهش یابد، ایمنی نویز برای تضمین یکپارچگی سیگنال مهمتر میشود. این مقاله یک روش بهبود ایمنی نویز کاربردی برای مدارهای زیرآستانه را ارائه میدهد. روش مرسوم برای افزایش ایمنی استفاده از یک اشمیتتریگر است که نیاز به یک مسیر جریان اضافی برای تنظیم ولتاژ آستانه سوئیچینگ دارد و حجم زیادی اشغال میکند. اگرچه، با استفاده از طرح VTMOS پیشنهادی، که ولتاژ آستانه ترانزیستورهای MOS را برای اجرای هیسترزیس ویژگیهای انتقال تنظیم میکند، هم منطقه و هم توان مصرفی میتواند به مقدار قابلتوجهی کاهش یابد و زمانیکه بهطور همزمان ایمنی نویز بهبود یافته، افزایش ناچیز در تاخیر، ایجاد می گردد. بنابرین، VTCMOS بر اساس طراحی منطقی دیجیتال میتواند طراحی IC کمتوان و مصونیت از نویز را فراهم سازد.

- بخشی از مقاله انگلیسی:

VI. CONCLUSION

As the supply voltage of a circuit decreases, noise immunity becomes more important to guarantee signal integrity. This paper presents a method of improving noise immunity applicable to subthreshold circuits. The traditional method for immunity enhancement is to use a Schmitt trigger, which requires an additional current path to adjust the switching threshold voltage and a large area. However, by utilizing the proposed VTMOS scheme, which adjusts the threshold voltage of the MOS transistor to implement the hysteresis of the transfer characteristics, both area and switching power consumption can be significantly reduced while simultaneously providing improved noise immunity, at the expense of a slight increase in delay. Therefore, the proposed VTCMOSbased digital logic design can enable noise-immune low-power IC design.

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

افزایش ایمنی الکترومغناطیسی پیشرفته مدارهای زیرآستانه با طراحی گیت های منطقی اشمیت تریگر منطقی با DTMOS |

| عنوان انگلیسی مقاله: |

Design of Schmitt Trigger Logic Gates Using DTMOS for Enhanced Electromagnetic Immunity of Subthreshold Circuits |

|

|