این مقاله انگلیسی ISI در نشریه ساینس دایرکت (الزویر) در 12 صفحه در سال 2016 منتشر شده و ترجمه آن 29 صفحه میباشد. کیفیت ترجمه این مقاله ویژه – طلایی ⭐️⭐️⭐️ بوده و به صورت کامل ترجمه شده است.

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

مسیریابی قابل تنظیم مجدد با توانایی تحمل خطا برای شبکه های درون تراشه ای با ساختار سلسله مراتب منطقی |

| عنوان انگلیسی مقاله: |

Reconfigurable fault tolerant routing for networks-on-chip with logical hierarchy |

|

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار | 2016 |

| تعداد صفحات مقاله انگلیسی | 12 صفحه با فرمت pdf |

| نوع مقاله | ISI |

| نوع نگارش | مقاله پژوهشی (Research Article) |

| نوع ارائه مقاله | ژورنال |

| رشته های مرتبط با این مقاله | مهندسی فناوری اطلاعات و کامپیوتر |

| گرایش های مرتبط با این مقاله | شبکه های کامپیوتری و معماری سیستم های کامپیوتری |

| چاپ شده در مجله (ژورنال) | کامپیوتر و مهندسی برق – Computers and Electrical Engineering |

| کلمات کلیدی | شبکه های درون تراشه ای (شبکه های درون یک تراشه)، سلسله مراتب، مسیریابی، تحمل خطا (تاب آوری خطا)، پیکربندی مجدد |

| کلمات کلیدی انگلیسی | Networks-on-chip – Hierarchy – Routing – Fault tolerance – Reconfiguration |

| ارائه شده از دانشگاه | گروه سیستم های جاسازی شده ، دانشگاه اشتوتگارت ، آلمان |

| نمایه (index) | Scopus – Master journals – JCR |

| نویسندگان | Gert Schley، Ibrahim Ahmed، Muhammad Afzal، Martin Radetzki |

| شناسه شاپا یا ISSN | ISSN 0045-7906 |

| شناسه دیجیتال – doi | https://doi.org/10.1016/j.compeleceng.2016.02.013 |

| ایمپکت فاکتور(IF) مجله | 2.762 در سال 2018 |

| شاخص H_index مجله | 49 در سال 2019 |

| شاخص SJR مجله | 0.443 در سال 2018 |

| شاخص Q یا Quartile (چارک) | Q2 در سال 2018 |

| بیس | نیست ☓ |

| مدل مفهومی | ندارد ☓ |

| پرسشنامه | ندارد ☓ |

| متغیر | ندارد ☓ |

| رفرنس | دارای رفرنس در داخل متن و انتهای مقاله ✓ |

| کد محصول | 9944 |

| لینک مقاله در سایت مرجع | لینک این مقاله در نشریه Elsevier |

| نشریه الزویر |  |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| وضعیت ترجمه | انجام شده و آماده دانلود در فایل ورد و PDF |

| کیفیت ترجمه | ویژه – طلایی ⭐️⭐️⭐️ |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش | 29 صفحه (شامل 1 صفحه رفرنس انگلیسی) با فونت 14 B Nazanin |

| ترجمه عناوین تصاویر و جداول | ترجمه شده است ✓ |

| ترجمه متون داخل تصاویر | ترجمه شده است ✓ |

| ترجمه متون داخل جداول | ترجمه شده است ✓ |

| درج تصاویر در فایل ترجمه | درج شده است ✓ |

| درج جداول در فایل ترجمه | درج شده است ✓ |

| منابع داخل متن | به صورت عدد درج شده است ✓ |

| منابع انتهای متن | به صورت انگلیسی درج شده است ✓ |

| فهرست مطالب |

|

چکیده |

| بخشی از ترجمه |

|

چکیده این مقاله یک مسیریابی قابل پیکربندی مجدد با قابلیت تحمل خطا را برای شبکه های درون تراشه ای (NoC) که در واحدهای سلسله مراتبی سازمان دهی شده اند ارائه می کند. در مواردی چون وجود خطا در لینک ارتباطی یا از کارافتادگی سوئیچ ها، روش پیشنهادی انطباق آنلاین مسیریابی را به صورت محلی در درون هر واحد امکان پذیر می سازد در حالی که آزادی بی وقفه به طور عمومی در شبکه تضمین می شود. نتایج تجربی حاصل از روش پیشنهادی برای یک شبکه 16x 16 افزایش سرعت به میزان تقریبا چهار برابری را برای پیکربندی مجدد مسیریابی در مقایسه با پیشرفته ترین روش نشان می دهد. ارزیابی با استفاده از خطاهای گذرا نشان می دهد که یک واحد اختصاصی با قابلیت پیکربندی مجدد، پیکربندی موفق جداول مسیریابی حتی در شریطی که احتمال خطا بالا است را امکان پذیر می سازد.

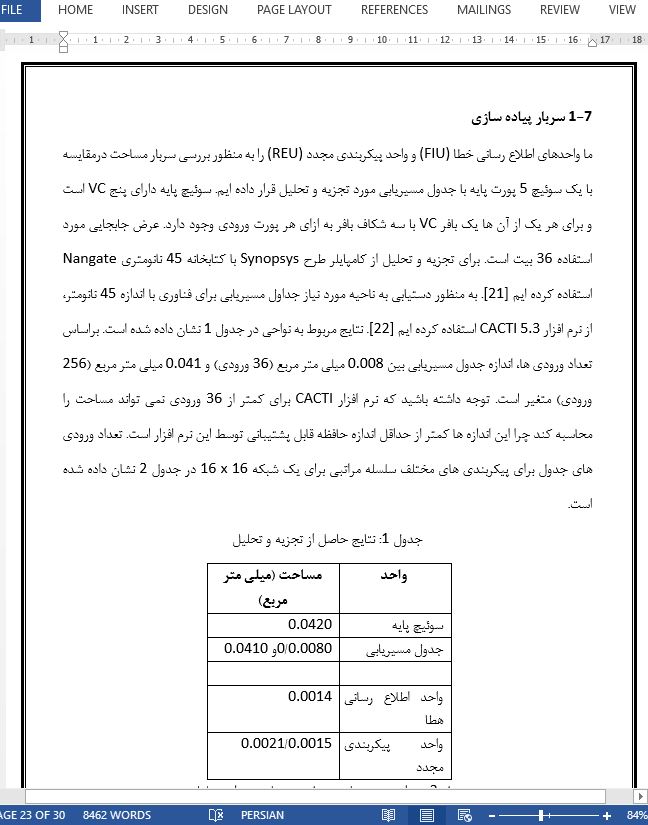

8- نتیجه گیری افزودن سلسله مراتب منطقی به شبکه های درون تراشه ای (NoC) مزیت های قابل توجهی را در مقایسه با NoC های با ساختار مسطح ارائه می کند. به ویژه، سلسله مراتب منطقی جداول مسیریابی را به یک طرح عملی تبدیل می کنند. این کار با داشتن تمامی ورودی های جدول تنها برای نودها در همان واحد منطقی شبکه و ادغام اطلاعات مسیرابی برای دیگر نودها از طریق انتزاع سلسله مراتبی به دست می آید. بنابراین، یک جدول مسیریابی برای یک سوئیچ در یک NoC با 256 نود نیازمند تنها کمتر از 20 درصد مساحت تراشه سوئیچ است در حالی که یک جدول کاملا پیاده سازی شده برای یک NoC مسطح نیازمند دو برابر مساحت یک سوئیچ است. علاوه بر این، نتایج ارزیابی برای یک توپولوژی مش 16 در 16 با سه سطح سلسله مراتب نشان می دهد که توان عملیاتی داده ها در مقایسه با توپولوژی شبکه غیر سلسله مراتبی دو برابر شده است. |

| بخشی از مقاله انگلیسی |

|

Abstract This paper presents a reconfigurable fault tolerant routing for Networks-on-Chip organized into hierarchical units. In case of link faults or failure of switches, the proposed approach enables the online adaptation of routing locally within each unit while deadlock freedom is globally ensured in the network. Experimental results of our approach for a 16 × 16 network show a speedup by a factor of almost four for routing reconfiguration compared to the state-of-the-art approach. Evaluation with transient faults shows that a dedicated reconfiguration unit enables successful reconfiguration of routing tables even in case of high error probabilities.

8- Conclusion Adding logical hierarchy to Networks-on-Chip (NoCs) offers significant benefits compared to NoCs with flat organization. In particular, logical hierarchy makes routing tables a feasible design choice. This is achieved by having full table entries only for nodes in the same logical network unit, and by merging routing information for other nodes through hierarchical abstraction. Thereby, a routing table for a switch in a 256 node NoC requires only less than 20% of the switch’s chip area, whereas a fully implemented table for a flat NoC would double the switch’s area. Furthermore, evaluation results for a 16 × 16 mesh topology with three hierarchy levels show that the data throughput is doubled compared to a non-hierarchical network topology. |

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

مسیریابی قابل تنظیم مجدد با توانایی تحمل خطا برای شبکه های درون تراشه ای با ساختار سلسله مراتب منطقی |

| عنوان انگلیسی مقاله: |

Reconfigurable fault tolerant routing for networks-on-chip with logical hierarchy |

|

|

|