| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

طراحی کارآمد و قدرتمند مساحت روتر شبکه بر روی تراشه از طریق استفاده از بافرهای خالی |

| عنوان انگلیسی مقاله: |

Power and Area Efficient Design of Network-on-Chip Router Through Utilization of Idle Buffers |

|

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار | 2010 |

| تعداد صفحات مقاله انگلیسی | 8 صفحه با فرمت pdf |

| رشته های مرتبط با این مقاله | مهندسی فناوری اطلاعات و کامپیوتر |

| گرایش های مرتبط با این مقاله | شبکه های کامپیوتری و معماری سیستم های کامپیوتری |

| چاپ شده در کنفرانس | کنفرانس بین المللی و کارگاه های آموزشی مهندسی سیستم های مبتنی بر کامپیوتر |

| ارائه شده از دانشگاه | گروه فناوری اطلاعات، دانشگاه تورکو، فنلاند |

| نویسندگان | Khalid Latif , Tiberiu Seceleanu , Hannu Tenhunen |

| شناسه شاپا یا ISBN | ISBN 978-1-4244-6538-5 |

| شناسه دیجیتال – doi | http://doi.org/10.1109/ECBS.2010.21 |

| رفرنس | دارد ✓ |

| کد محصول | 9326 |

| لینک مقاله در سایت مرجع | لینک این مقاله در سایت IEEE |

| نشریه آی تریپل ای | |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| وضعیت ترجمه | انجام شده و آماده دانلود |

| کیفیت ترجمه | طلایی⭐️ |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش | 19 صفحه با فونت 14 B Nazanin |

| ترجمه عناوین تصاویر و جداول | ترجمه شده است ✓ |

| ترجمه متون داخل تصاویر | ترجمه نشده است ☓ |

| ترجمه متون داخل جداول | ترجمه نشده است ☓ |

| درج تصاویر در فایل ترجمه | درج شده است ✓ |

| درج جداول در فایل ترجمه | درج شده است ✓ |

| منابع داخل متن | به صورت عدد درج شده است ✓ |

| فهرست مطالب |

|

چکیده 1 مقدمه کار مرتبط 2 انگیزه 3 معماری پیشنهادی مسیریاب 3.1 نوع بسته 3.2 کنترل کننده ورودی و تخصیص بافر 3.3 کنترل کننده خروجی و الگوریتم مسیریابی 3.4 مقایسه با معماری های موجود 3.5 پیاده سازی 4 نتایج تجربی 5 بررسی 6 نتیجه گیری ها کار آینده |

| بخشی از ترجمه |

|

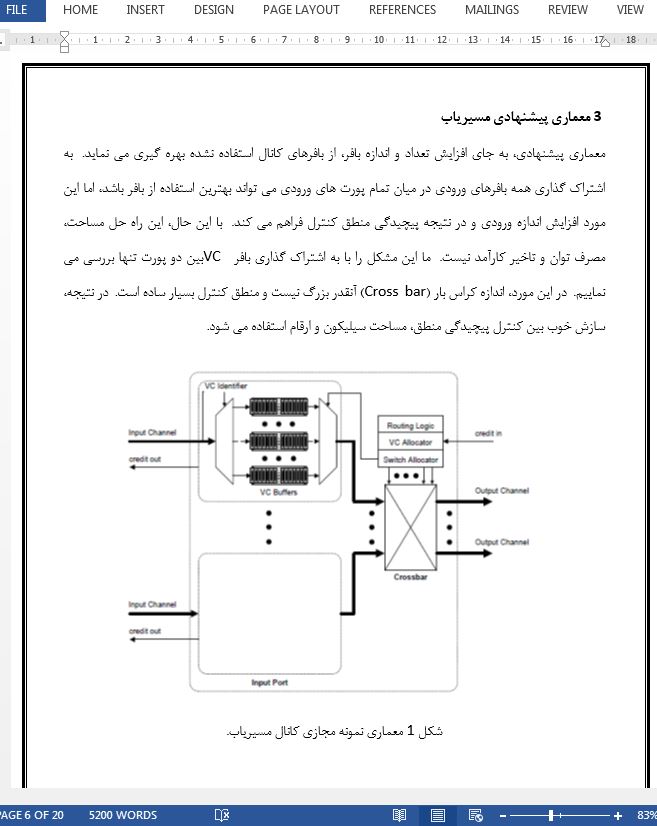

چکیده شبکه بر روی تراشه (NOC) ، پلت فرم اتصال داخلی است که به الزامات طراحی روی تراشه مدرن پاسخ می دهد. بهینه سازی های کوچک در معماری مسیریاب NoC می تواند بهبود قابل توجهی را در عملکرد کلی سیستم های مبتنی بر NoC نشان دهد. مصرف توان، سربار مساحت و عملکرد کلی NoC توسط بافر مسیریاب تحت تاثیر قرار می گیرد. به اشتراک گذاری منابع برای شبکه بر روی تراشه برای کاهش مساحت تراشه و مصرف انرژی مهم است. به اشتراک گذاری مجازی بافر کانال توسط دیگر پورت های مسیریاب به منظور ارتقای عملکرد در تراشه های ارتباطی مطرح شده است. ما رویکرد بهینه سازی معماری مسیریاب را با استفاده از بافرهای غیر فعال برای افزایش تعداد و اندازه بافر برای توان عملیاتی مورد نظر را در نظر می گیریم.

6 نتیجه گیری ها در عصر سیلیکون در حال حاضر، NoC در توان و مساحت مقرون به صرفه نیست هر چند دارای توان عملیاتی بالاتر است. ارتقا در استفاده از منابع غیر فعال به جای قرار دادن امکانات جدید، NoC را به یک راه حل ایده آل برای برنامه های کاربردی فعلی تبدیل ساخته است. نمونه اولیه طراحی شده بر اساس اجزای پارامتری و سنتز شده است که شامل کنترل کننده های FIFO ورودی و خروجی، تخصیص دهنده بافر، کراس بار خروجی (Cross bar) و عنصر محاسبه مسیر می شود. با توجه به ماهیت توزیع شده معماری ارائه شده، افزایش تعداد پورت ها، یک مسئله نیست و از این رو می تواند در پیاده سازی یک NoC سه بعدی و یا درج های لینک دور برد [18] استفاده می شود. |

| بخشی از مقاله انگلیسی |

|

Abstract Network-on-Chip (NoC) is the interconnection platform that answers the requirements of the modern on-Chip design. Small optimizations in NoC router architecture can show a significant improvement in the overall performance of NoC based systems. Power consumption, area overhead and the entire NoC performance is influenced by the router buffers. Resource sharing for on-chip network is critical to reduce the chip area and power consumption. Virtual channel buffer sharing by other router ports has been proposed to enhance the performance of on-chip communication. We approach the router architecture optimization by utilizing the idle buffers instead of increasing the number and size of buffers for desired throughput.

6 Conclusions In the current silicon era, NoC is not power and area efficient although it has higher throughput. Enhancement in the utilization of idle resources instead of inserting new ones can make the NoC an ideal solution for current applications. The designed prototype is based on parameterized and synthesized components which include FIFO’s, input and output controllers, buffer allocator, output crossbar and route computation element. Due to the distributed nature of proposed architecture, increasing the number of ports is not an issue and hence it can be used in the implementation of a 3D NoC or long-range link insertions [18].

|

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

طراحی کارآمد و قدرتمند مساحت روتر شبکه بر روی تراشه از طریق استفاده از بافرهای خالی |

| عنوان انگلیسی مقاله: |

Power and Area Efficient Design of Network-on-Chip Router Through Utilization of Idle Buffers |

|

|

|