| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

یک ADC سابرنجینگ درون یابی شده 6 بیتی، GS/s 1 و 9.9 میلی واتی در CMOS 65 نانومتری |

| عنوان انگلیسی مقاله: |

A 6-bit, 1-GS/s, 9.9-mW, Interpolated Subranging ADC in 65-nm CMOS |

|

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار | 2014 |

| تعداد صفحات مقاله انگلیسی | 10 صفحه با فرمت pdf |

| نوع مقاله | ISI |

| نوع ارائه مقاله | ژورنال |

| رشته های مرتبط با این مقاله | مهندسی برق |

| گرایش های مرتبط با این مقاله | مدارهای مجتمع الکترونیک، مهندسی الکترونیک و سیستم های قدرت |

| چاپ شده در مجله (ژورنال) | مجله مدارهای حالت جامد – Journal of Solid-State Circuits |

| کلمات کلیدی | مدارهای مجتمع آنالوگ CMOS، کالیبراسیون پیش زمینه، تبدیل آنالوگ – دیجیتال، درون یابی، سابرنجینگ یا زیرمحدوده یابی |

| کلمات کلیدی انگلیسی | Analog–digital conversion – CMOS analog integrated circuits – foreground calibration – interpolation – subranging |

| ارائه شده از دانشگاه | ژاپن |

| نمایه (index) | Scopus – JCR |

| نویسندگان | Takumi Danjo، Masato Yoshioka، Masayuki Isogai، Masanori Hoshino، and Sanroku Tsukamoto |

| شناسه شاپا یا ISSN | ISSN 0018-9200 |

| شناسه دیجیتال – doi | https://doi.org/10.1109/JSSC.2013.2297416 |

| ایمپکت فاکتور(IF) مجله | 5.542 در سال 2018 |

| شاخص H_index مجله | 197 در سال 2019 |

| شاخص SJR مجله | 2.004 در سال 2018 |

| شاخص Q یا Quartile (چارک) | Q1 در سال 2018 |

| بیس | است ✓ |

| مدل مفهومی | دارد ✓ |

| پرسشنامه | ندارد ☓ |

| متغیر | ندارد ☓ |

| رفرنس | دارای رفرنس در داخل متن و انتهای مقاله ✓ |

| کد محصول | 9828 |

| لینک مقاله در سایت مرجع | لینک این مقاله در سایت IEEE |

| نشریه آی تریپل ای | |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| وضعیت ترجمه | انجام شده و آماده دانلود در فایل ورد و PDF |

| کیفیت ترجمه | طلایی⭐️ |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش | 21 صفحه با فونت 14 B Nazanin |

| ترجمه عناوین تصاویر و جداول | ترجمه شده است ✓ |

| ترجمه متون داخل تصاویر | ترجمه شده است ✓ |

| ترجمه متون داخل جداول | ترجمه شده است ✓ |

| درج تصاویر در فایل ترجمه | درج شده است ✓ |

| درج جداول در فایل ترجمه | درج شده است ✓ |

| درج فرمولها و محاسبات در فایل ترجمه | به صورت عکس درج شده است ✓ |

| منابع داخل متن | به صورت عدد درج شده است ✓ |

| منابع انتهای متن | به صورت انگلیسی درج شده است ✓ |

| فهرست مطالب |

|

چکیده |

| بخشی از ترجمه |

|

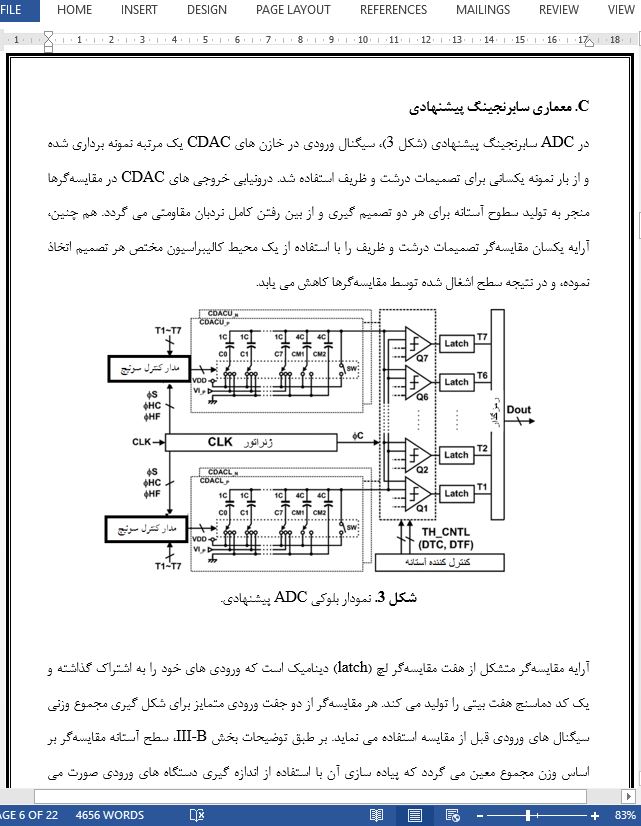

چکیده یک مبدل آنالوگ به دیجیتال (ADC) سابرنجینگ 6 بیتی، GS/s 1 پیاده شده در CMOS 65 نانومتری توسعه داده شد. از مبدل دیجیتال به آنالوگ با خازن (CDAC) مشابه برای نمونه برداری از سیگنال های آنالوگ و در نتیجه از بین بردن خطاهای بین تصمیمات درشت و ظریف که هنگام کاربرد دو نمونهبردار مختلف برای گرفتن سیگنال رخ می دهد، استفاده گردید. هر دو تصمیم گیری از مقایسهگرهای یکسانی استفاده نموده، و از یک مدار کالیبراسیون دیجیتالی برای جبران خطاهای موجود در سطوح آستانه مختلف برای دو تصمیم گیری استفاده شد. این کالیبراسیون منجر به از بین بردن مقایسهگرهای اضافی و در نتیجه کاهش سطح می گردد. ژنراتورهای ولتاژ مرجع که با استفاده از نردبان های مقاومت در ADC سابرنجینگ معمولی پیاده می شوند، به لطف استفاده از CDAC همراه با درونیابی در مقایسهگرها حذف می گردند. این امر منجر به حل و فصل دو مشکل مربوط به نردبان مقاومت یعنی: موازنه بین زمان نشست و مصرف جریان استاتیک و سیگنال وابسته به مقاومت سوئیچ های متصل به گره های پتانسیل میانی می گردد. یک تراشه آزمون ساخته شده با فناوری CMOS 65 نانومتری در GS/s 1 و با SNDR (نسبت سیگنال به نویز) معادل 32.8 دسی بل کار می کند. سطح فعال آن 0.044 میلی متر مربع بوده و مصرف برق آن 9.9 میلی وات و با ولتاژ تغذیه 1.1 ولت می باشد.

V- نتیجه گیری یک معماری سابرنجینگ پیشرفته برای مقابله با مسائل ناشی از زمان نشست ولتاژهای مرجع و سوئیچ متصل به گره های پتانسیل میانی در سابرنجینگ ADC پیشنهاد شد. در این معماری ADC، ژنراتور با ولتاژ مرجع و سوئیچ های همراه آن با استفاده از CDAC حذف شده و سطح آستانه مقایسهگرها به صورت دیجیتالی با استفاده از درونیابی فعال کنترل گردید. افزون بر این، برای کاهش سطح ADC و خطای نمونه برداری، از مجموعه مقایسهگرهای یکسانی (هیچ مقایسهگر اضافی وجود نداشت) برای تصمیمات درشت و ظریف استفاده گردیده است. برای تحقق بخشیدن به این معماری، کدهای کنترل آستانه مختلفی برای تصمیمات درشت و ظریف به ازای هر مقایسهگر عرضه شد. یک مدار کنترل دیجیتالی کمکی با ایجاد یک ولتاژ اسمی با CDAC به کد کنترل آستانه مخصوص تصمیم درشت دست می یابد. کد مخصوص تصمیم گیری ظریف بر اساس محاسبه دیجیتالی و با استفاده از کد درشت به جای استفاده از یک DAC با وضوح بالا به دست می آید، و کلیه کالیبراسیون ها معمولاً رو تراشه ای انجام می شوند. |

| بخشی از مقاله انگلیسی |

|

Abstract A 6-bit, 1-GS/s subranging analog-to-digital converter (ADC) implemented in 65-nm CMOS is developed. The same capacitor DACs (CDACs) are used to sample the analog signals, thereby eliminating the errors between the coarse and fine decisions that occur when two different samplers are used to capture the signal. Both decisions use the same comparators, and a digitally assisted calibration circuit compensates for the errors in the different threshold levels used for the two decisions. This calibration eliminates redundant comparators, and thus, reduces the area. Reference voltages generators, which are implemented using resistor ladders in conventional subranging ADCs, are eliminated thanks to the use of the CDACs together with interpolation in the comparators. This solves two problems related to the resistor ladder, namely, the trade-off between the settling time and the static-current consumption and signal dependent on-resistance of switches connected to intermediate potential nodes. A test chip fabricated in 65-nm CMOS technology operates at 1 GS/s with SNDR of 32.8 dB. Its active area is 0.044 mm 2 , and its power consumption is 9.9 mW at a 1.1-V supply voltage.

V- CONCLUDING REMARKS An improved subranging architecture was proposed to deal with issues caused by the settling time of the reference voltages and switches connected to intermediate potential nodes in subranging ADCs. In this ADC architecture, the reference-voltage generator and its accompanying switches are eliminated by the use of CDACs and the comparators’ threshold level is digitally controlled by means of active interpolation. In addition, to reduce the area of the ADC and sampling error, the same set of comparators (there are no redundant comparators) is used for the coarse and fine decisions. To realize this architecture, different threshold-control codes for the coarse and fine decisions are supplied to each comparator. A digitally assisted control circuit obtains the threshold-control code for the coarse decision by generating an nominal voltage with the CDACs. The code for the fine decision is obtained by digital calculation using the coarse code rather than by using a high-resolution DAC, and all the calibrations are done on-chip. |

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

یک ADC سابرنجینگ درون یابی شده 6 بیتی، GS/s 1 و 9.9 میلی واتی در CMOS 65 نانومتری |

| عنوان انگلیسی مقاله: |

A 6-bit, 1-GS/s, 9.9-mW, Interpolated Subranging ADC in 65-nm CMOS |

|

|

|