این مقاله انگلیسی ISI در نشریه IEEE در 2 صفحه در سال 2017 منتشر شده و ترجمه آن 6 صفحه میباشد. کیفیت ترجمه این مقاله ویژه – طلایی ⭐️⭐️⭐️ بوده و به صورت کامل ترجمه شده است.

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

یک مقایسه دیفرانسیل توان کم، پر سرعت، آفست کم و برای مبدل های آنالوگ به دیجیتال |

| عنوان انگلیسی مقاله: |

A High-Speed, Low-Offset and Low-Power Differential Comparator for Analog to Digital Converters |

|

|

|

| مشخصات مقاله انگلیسی | |

| فرمت مقاله انگلیسی | |

| سال انتشار | 2017 |

| تعداد صفحات مقاله انگلیسی | 2 صفحه با فرمت pdf |

| نوع مقاله | ISI |

| نوع ارائه مقاله | کنفرانس |

| رشته های مرتبط با این مقاله | مهندسی برق |

| گرایش های مرتبط با این مقاله | مهندسی الکترونیک، سیستم های قدرت، سیستمهای الکترونیک دیجیتال |

| چاپ شده در کنفرانس | کنفرانس بین المللی طراحی SoC |

| کلمات کلیدی | مقایسه کننده سرعت بالا، آفست کم، توان پایین، نویز kickback پایین |

| کلمات کلیدی انگلیسی | High speed comparator – low offset – low power – low kickback noise |

| ارائه شده از دانشگاه | گروه مهندسی برق، دانشگاه ایالتی سن خوزه، ایالات متحده آمریکا |

| نویسندگان | Mehdi Nasrollahpour, Chi-Hsien Yen, Sotoudeh Hamedi-hagh |

| شناسه دیجیتال – doi | https://doi.org/10.1109/ISOCC.2017.8368862 |

| بیس | نیست ☓ |

| مدل مفهومی | ندارد ☓ |

| پرسشنامه | ندارد ☓ |

| متغیر | ندارد ☓ |

| رفرنس | دارای رفرنس در داخل متن و انتهای مقاله ✓ |

| کد محصول | 10845 |

| لینک مقاله در سایت مرجع | لینک این مقاله در سایت IEEE |

| نشریه آی تریپل ای | |

| مشخصات و وضعیت ترجمه فارسی این مقاله | |

| فرمت ترجمه مقاله | pdf و ورد تایپ شده با قابلیت ویرایش |

| وضعیت ترجمه | انجام شده و آماده دانلود |

| کیفیت ترجمه | ویژه – طلایی ⭐️⭐️⭐️ |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش | 6 (1 صفحه رفرنس انگلیسی) صفحه با فونت 14 B Nazanin |

| ترجمه عناوین تصاویر و جداول | ترجمه شده است ✓ |

| ترجمه متون داخل تصاویر | ترجمه نشده است ☓ |

| ترجمه متون داخل جداول | ترجمه نشده است ☓ |

| ترجمه ضمیمه | ندارد ☓ |

| ترجمه پاورقی | ندارد ☓ |

| درج تصاویر در فایل ترجمه | درج شده است ✓ |

| درج جداول در فایل ترجمه | درج شده است ✓ |

| درج فرمولها و محاسبات در فایل ترجمه | به صورت عکس درج شده است ✓ |

| منابع داخل متن | به صورت عدد درج شده است ✓ |

| منابع انتهای متن | به صورت انگلیسی درج شده است ✓ |

| فهرست مطالب |

|

چکیده 1- مقدمه 2- پیادهسازی مدار مقایسه کننده پیشنهادی 3- نتایج شبیهسازی 4- خلاصه |

| بخشی از ترجمه |

|

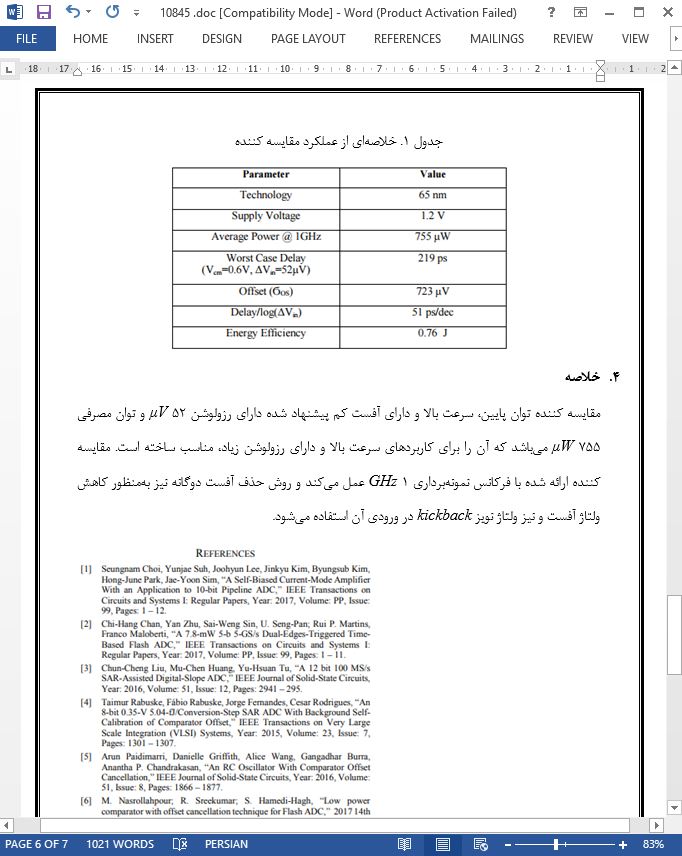

چکیده آنالیز و طراحی یک مقایسه کننده سرعت بالا با آفست ورودی اصلاح شده در این مقاله ارائه میشود. مقایسه کننده پیشنهادی تحت فناوری CMOS ی توان پایین TSMC با ولتاژ تغذیه 1.2 V طراحی میشود. مقایسه کننده ارائه شده جدید دارای مصرف توان پایینی بوده و از روش حذف آفست دوگانه استفاده میکند. حداقل ولتاژ ورودی قابلتبدیل برابر 52 μV محاسبه میشود و تأخیر انتشار نیز در این حالت برابر 2019 ps است. مصرف توان در فرکانس کلاک 1 GHz برابر 755 μW است. شبیهسازی مونتکارلو با 500 تکرار نشان میدهد که انحراف استاندارد آفست ورودی حدود 723 μV است.

مقدمه مقایسه کنندهها، مهمترین نقش را در مبدلهای آنالوگ به دیجیتال مبتنی بر ولتاژ (ADCs) نظیر رجیستر تقریب متوالی (SAR)، خط لولهای، و بهخصوص در ADCs ی فلاش [1-3] ایفا میکنند. طراحی مقایسه کنندهها تحت توان تغذیه پایین با سرعت بالاتر و توان مصرفی پایینتر دارای چالشهای خاص خود است. علاوه بر این، پیادهسازی مدارها تحت فناوریهای کمتر از نانوی CMOS به مدارهای دیجیتالی کمکی و روشهای پیچیده برای غلبه بر نویز kickback و ولتاژ آفست نیاز دارد [4-6]. نویز kickback و تغییرات آفست ناشی از وجود مسیر خازنی در ورودی میتواند باعث تضعیف عملکرد کلی سیستم شود، مثلاً ممکن است سطوح ولتاژ رفرنس را در ADC های فلاش شیفت دهد. این تضعیف ناشی از پروسه تبدیل اشتباه میباشد.

خلاصه مقایسه کننده توان پایین، سرعت بالا و دارای آفست کم پیشنهاد شده دارای رزولوشن 52 μV و توان مصرفی 755 μW میباشد که آن را برای کاربردهای سرعت بالا و دارای رزولوشن زیاد، مناسب ساخته است. مقایسه کننده ارائه شده با فرکانس نمونهبرداری 1 GHz عمل میکند و روش حذف آفست دوگانه نیز بهمنظور کاهش ولتاژ آفست و نیز ولتاژ نویز kickback در ورودی آن استفاده میشود. |

| بخشی از مقاله انگلیسی |

|

Abstract Analysis and design of a high-speed comparator with improved input referred offset is presented in this paper. The proposed comparator is designed in TSMC low power CMOS technology under 1.2 V power supply. The new presented comparator has a low power consumption and utilizes dual offset cancellation technique. The minimum convertible input voltage is calculated to be 52 μV and the propagation delay at this worst case is equal to 219 ps. The power consumption at 1 GHz clock frequency is 755 μW. Monte Carlo simulation with 500 points iteration shows that the standard deviation of the input referred offset is about 723 μV.

INTRODUCTION Comparators play the most important role in voltage based analog to digital converters (ADCs) such as successive approximation register (SAR), Pipeline, and specifically in Flash ADCs [1-3]. Designing the comparators in the lower power supply with higher speed and lower power has its own challenges. Besides, realizing circuits in sub-nano CMOS technologies need digitally assisted circuits and complex techniques to overcome the kickback noise and offset voltage [4- 6]. The kickback noise and offset variation due to the capacitive path to the input can degrade the overall performance of the system, e.g., it can shift the different reference voltage levels in Flash ADC. This degradation will result in the erroneous conversion process.

SUMMARY The proposed high-speed, low-offset, low-power comparator has a resolution of 52 ȝV and a power consumption of 755 ȝW which make this comparator suitable for high resolution and fast applications. The presented comparator works with a 1 GHz sampling frequency where a dual offset cancellation technique is applied to reduce the offset voltage and kickback noise voltage to the input. |

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

یک مقایسه دیفرانسیل توان کم، پر سرعت، آفست کم و برای مبدل های آنالوگ به دیجیتال |

| عنوان انگلیسی مقاله: |

A High-Speed, Low-Offset and Low-Power Differential Comparator for Analog to Digital Converters |

|

|

|