این مقاله انگلیسی ISI در نشریه IEEE در 5 صفحه در سال 2016 منتشر شده و ترجمه آن 11 صفحه میباشد. کیفیت ترجمه این مقاله ویژه – طلایی ⭐️⭐️⭐️ بوده و به صورت کامل ترجمه شده است.

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

اجرای مدل TFET SPICE برای تجزیه و تحلیل مدارهای بسیار کم توان |

| عنوان انگلیسی مقاله: |

Implementation of TFET SPICE Model for Ultra-Low Power Circuit Analysis |

|

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار | 2016 |

| تعداد صفحات مقاله انگلیسی | 5 صفحه با فرمت pdf |

| نوع مقاله | ISI |

| نوع ارائه مقاله | ژورنال |

| رشته های مرتبط با این مقاله | مهندسی برق |

| گرایش های مرتبط با این مقاله | سیستم های قدرت، مدارهای مجتمع پیچیده، مهندسی الکترونیک |

| چاپ شده در مجله (ژورنال) | مجله جامعه دستگاههای الکترونی – Journal of the Electron Devices Society |

| کلمات کلیدی | ترانزیستور های اثر میدان، SPICE، مدل سازی دستگاه های نیمه رسانا |

| کلمات کلیدی انگلیسی | SPICE – semiconductor device modeling – field effect transistors |

| ارائه شده از دانشگاه | مرکز تحقیق و توسعه شرکت ، توشیبا ، ژاپن |

| نمایه (index) | Scopus –DOAJ – JCR |

| نویسندگان | CHIKA TANAKA، KANNA ADACHI، MOTOHIKO FUJIMATSU، AKIRA HOKAZONO، YOSHIYUKI KONDO AND SHIGERU KAWANAKA |

| شناسه شاپا یا ISSN | ISSN 2168-6734 |

| شناسه دیجیتال – doi | https://doi.org/10.1109/JEDS.2016.2550606 |

| ایمپکت فاکتور(IF) مجله | 2.167 در سال 2018 |

| شاخص H_index مجله | 23 در سال 2019 |

| شاخص SJR مجله | 0.643 در سال 2018 |

| شاخص Q یا Quartile (چارک) | Q2 در سال 2018 |

| بیس | است ✓ |

| مدل مفهومی | دارد ✓ |

| پرسشنامه | ندارد ☓ |

| متغیر | ندارد ☓ |

| رفرنس | دارای رفرنس در داخل متن و انتهای مقاله ✓ |

| کد محصول | 9795 |

| لینک مقاله در سایت مرجع | لینک این مقاله در سایت IEEE |

| نشریه آی تریپل ای | |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| وضعیت ترجمه | انجام شده و آماده دانلود در فایل ورد و PDF |

| کیفیت ترجمه | ویژه – طلایی ⭐️⭐️⭐️ |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش | 11 صفحه (شامل 1 صفحه رفرنس انگلیسی) با فونت 14 B Nazanin |

| ترجمه عناوین تصاویر و جداول | ترجمه شده است ✓ |

| ترجمه متون داخل تصاویر | ترجمه نشده است ☓ |

| ترجمه متون داخل جداول | ترجمه شده است ✓ |

| درج تصاویر در فایل ترجمه | درج شده است ✓ |

| درج جداول در فایل ترجمه | درج شده است ✓ |

| درج فرمولها و محاسبات در فایل ترجمه | به صورت عکس درج شده است ✓ |

| منابع داخل متن | درج نشده است ☓ |

| منابع انتهای متن | به صورت انگلیسی درج شده است ✓ |

| فهرست مطالب |

|

چکیده 1- مقدمه 2- مدل سازی دستگاه الف) مدل MOSFET ب) مدل سازی های TFET 3- ارزیابی مدل 4- جمع بندی |

| بخشی از ترجمه |

|

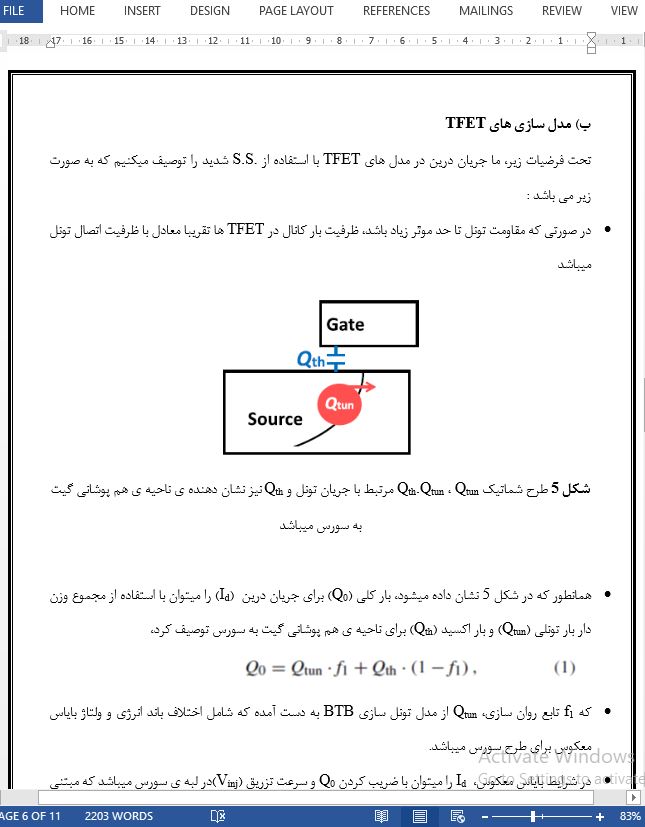

چکیده ما در این مقاله یک مدل فشرده برای ترانزیستور های تاثیر میدان تونلی (TFET) را ارائه کرده ایم، که تخمین کانال های مختلف را ترکیب میکند. بار کلی برای جریان تخلیه ، با استفاده از مجموع وزن دار بار تونلی و بار اکسید برای ناحیه ی همپوشانی گیت بر روی سورس، توصیف شده است. برای به دست آوردن مدل فشرده ی TFET برای شبیه سازی مدار هایی که در تمام منطقه های ولتاژی فعالیت میکند، جریان عملیاتی تحت این ولتاژ گیت به سورس و شرایط ولتاژ درین به سورس در این مطالعه در نظر گرفته شده است. Verilog ، که یک توصیف برای مدل پیشنهاد شده ی ما است، در یک شبیه ساز مدار اجرا شده است. پارامتر های مدل برای ساختار های متداول TFET ، با مقایسه ی نتایج شبیه سازی های دو بعدی TCAD ، به دست آمده است. بعد از تایید این شبیه سازی ها در سطح ترانزیستور، شبیه سازی های سطح مدار با نوسان کننده ی حلقه ای 81 مرحله ای با استفاده از مدل ما، انجام میشود.

4- جمع بندی در این مطالعه، مدل فشرده برای TFET ها ، که از BSIM4 استفاده میکند، ارائه شده است. برای به دست آوردن مدل های فشرده ی TFET برای شبیه سازی مدار که در هر ناحیه ی ولتاژ اعمال میشود، جریان عملیاتی تحت Vgs و Vds در نظر گرفته میشود. پارامتر های مدل برای جریان تونل BTB، جریان نشتی برای TFET های متداول استخراج شده است و در این روند از مقایسه ی نتایج دو بعدی TCAD استفاده شده است . در این روند، S.S. های شدید کمتر از 60mV در هر ده دوره و پیوستگی ناحیه ی انتقال از حالت معکوس ضعیف تا معکوس قوی مورد بررسی قرار گرفته است. شبیه سازی های سطح مدار با نوسان کننده های حلقه ای 81 مرحله ای با استفاده از مدل ها، اجرا شده است. ازین رو، مدل پیشنهاد شده ی ما یک ابزار مفید برای توصیف عملکرد مدارهای فوق کم توان بر روی TFET میباشد. |

| بخشی از مقاله انگلیسی |

|

Abstract We proposed a compact model for tunneling field effect transistors (TFETs), which combines BSIM4. Our proposed model for tunneling current is based on a drift-diffusion model under the gradual-channel approximation. The total charge for the drain current has been described by a weighted sum of the tunneling charge and the oxide charge for gate-to-source overlap region. In order to obtain TFETs compact model for circuit simulation that operates in every voltage region, the operating current under the various gate-to-source voltage and drain-to-source voltage conditions are considered. Verilog-A description for our proposed model are implemented in the circuit simulator. Model parameters are extracted for conventional TFETs structure by comparing with in-house 2-D TCAD simulation results. After the transistor-level verification, the circuit-level simulation of 81-stage ring-oscillator using our proposed model has been performed.

IV- CONCLUSION In this study, the compact model of TFETs, which combines BSIM4, has been proposed. In order to obtain TFETs compact model for circuit simulation that operates in every voltage region, the operating current under the various Vgs and Vds conditions are considered. Model parameters for BTB tunneling current, leakage current were extracted for the conventional TFETs structure by comparing with 2D TCAD simulation results. In our formation, the steep S.S. less than 60mV/decade and the continuity of transition region from weak inversion to strong inversion have been expressed. The circuit-level simulation of 81-stage ring-oscillator using our proposed model was performed. Therefore, our proposed model will be a useful tool for characterizing an ultra-low circuit performance of TFETs. |

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی | |

| عنوان فارسی مقاله: |

اجرای مدل TFET SPICE برای تجزیه وتحلیل مدار های بسیار کم توان |

| عنوان انگلیسی مقاله: |

Implementation of TFET SPICE Model for Ultra-Low Power Circuit Analysis |

|

|

|