گروه آموزشی ترجمه فا اقدام به ارائه ترجمه مقاله با موضوع ” طراحی latch مقاوم در برابر تابش بالا در فناوری CMOS 65nm ” در قالب فایل ورد نموده است که شما عزیزان میتوانید پس از دانلود رایگان مقاله انگلیسی و نیز مطالعه نمونه ترجمه و سایر مشخصات، ترجمه را خریداری نمایید.

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

طراحی یک latch چفت شده کم هزینه و با تشعشع قابل اطمینان بالا توسط فناوری 66 nm CMOS |

| عنوان انگلیسی مقاله: |

Low cost and highly reliable radiation hardened latch design in 65 nm CMOS technology |

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار | 2015 |

| تعداد صفحات مقاله انگلیسی | 10 صفحه با فرمت pdf |

| رشته های مرتبط با این مقاله | مهندسی برق |

| گرایش های مرتبط با این مقاله | افزاره های میکرو و نانو الکترونیک، مهندسی الکترونیک و مکاترونیک |

| مجله | اعتبار میکرو الکترونیک – Microelectronics Reliability |

| دانشگاه | مرکز میکروالکترونیک، مؤسسه فناوری هاربین، چین |

| کلمات کلیدی | لنز سخت رادیاتور، قابلیت اطمینان، SEU، گذار تک رویداد (SET) |

| شناسه شاپا یا ISSN | 2015.03.014 ISSN |

| رفرنس | دارد |

| لینک مقاله در سایت مرجع | لینک این مقاله در نشریه Elsevier |

| نشریه | Elsevier |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش و فونت 14 B Nazanin | 22 صفحه |

| ترجمه عناوین تصاویر و جداول | ترجمه شده است |

| ترجمه متون داخل تصاویر | ترجمه نشده است |

| ترجمه متون داخل جداول | ترجمه نشده است |

| درج تصاویر در فایل ترجمه | درج شده است |

| درج جداول در فایل ترجمه | درج شده است |

| درج فرمولها و محاسبات در فایل ترجمه به صورت عکس | درج شده است |

- فهرست مطالب:

خلاصه

1. مقدمه

2. کارهای پیشین

3. طراحی latch چفت شده پیشنهادی

5. اثرات ولتاژ منبع تغذیه، درجه حرارات و پردازش

6. نتیجه گیری

- بخشی از ترجمه:

6. نتیجه گیری

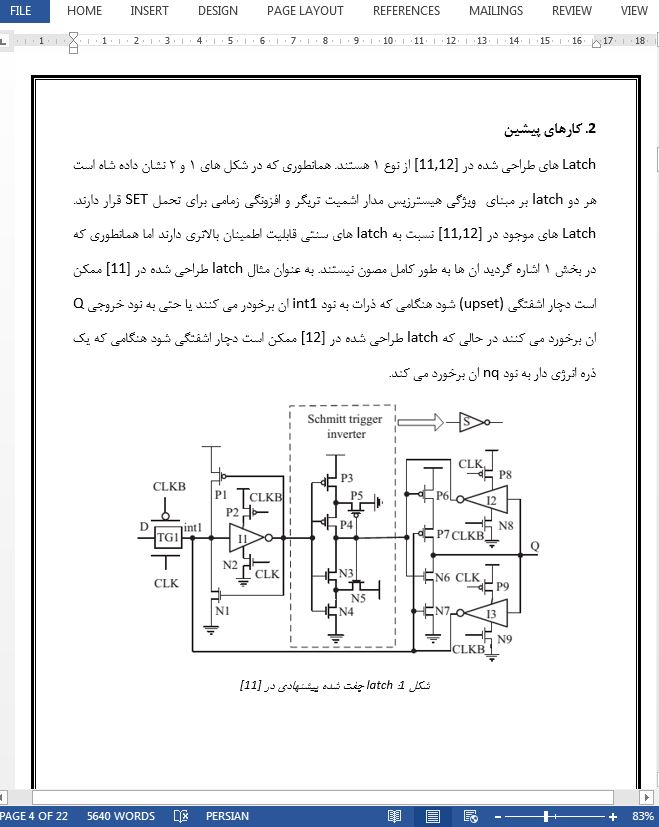

در این مقاله یک مدار latch چفت شده ارزان قیمت با قابلیت اطمینان بالا در مقابل تشعشع پیشنهاد داده شده است که توسط فناروی تجاری 65 nm پیاده سازی شده است. بر اساس طراحی ساختار منطقی، latch پیشنهادی به طور از نظر SEU مصون است که به معنای ان است که می تواند یک SEU را بر روی هر یک از نود های منفرد داخلی اش تحمل کند. علاوه بر این latch پیشنهادی قابلیت فیلترینگ SET را نیز دارد. بنابراین latch پیشنهادی نه تنها خطا های نرم (کم شدت) حاصل شده توسط SET های ورودی در بخش های پیوندی (ترکیبی) را تحمل می کند بلکه همچنین می تواند SEU های داخلی در بخش های پشت سر هم (متوالی) را نیز تحمل نماید. Latch پیشنهادی همچنین بر مساله رسیدن به حالت امپدانسی بالا در هنگامی که یک ذره بر روی نود های داخلی اش برخورد می کند، غلبه کرده است. در مقایسه با latch هیا نوع 4، latch پیشنهادی ما دارای ویژگی حداقل به ترتیب 39% و 67.6% کاهش در مصرف توان و محصول تاخیر توان (PDP) است. به بیان دیگر latch پیشنهادی ما دارای کمترین مصرف توان و محصول تاخیر توان در میان latch های نوع 4 است در حالی که دارای رتبه دوم از نظر کمترین سربار محیطی است و قابل رقابت با سایر latch ها از نظر تحمل SEMU ها می باشد. اثرات تغییرات پردازش، ولتاژ منبع تغذیه و درجه حرارت بر روی latch پیشنهادی نیز مورد بررسی قرار گرفته است که نشان می دهد latch پیشنهادی حساسیت کمتری به ولتاژ و پردازش دارد.

- بخشی از مقاله انگلیسی:

6. ConclusionThis

paper has proposed a low cost and highly reliable radiationhardened latch circuit which is implemented in 65 nm commercialtechnology. By reasonable structure design, the proposed latch isfully SEU immune which means that it can tolerate an SEU onany one of its internal single node. In addition, the proposed latchis capable of SET filtering. Hence, the proposed latch not only cantolerate the soft errors caused by input SETs in combinationalparts, but also can tolerate internal SEUs in sequential parts. Theproposed latch has also overcome the problem of taking a highimpedance state when a particle strikes on some of its internalnodes. Compared with the latches of type 4, our proposed latchfeatures at least 39% and 67.6% reduction of power consumptionand power delay product, respectively, in other words, our proposedlatch has the lowest power consumption and power delayproduct among the latches of type 4, while it features a secondlowest area overhead and has a comparable ability of SEMUs tolerance.The impacts of process, supply voltage and temperaturevariation on proposed latch are also investigated, which shows thatour proposed latch is less sensitive to voltage and process.

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

طراحی latch سفت شده و کم هزینه مقاوم در برابر تابش بسیار بالا در فناوری CMOS 65nm |

| عنوان انگلیسی مقاله: |

Low cost and highly reliable radiation hardened latch design in 65 nm CMOS technology |

|

|