| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

طراحی و بهینه سازی مدارهای CMOS آستانه دوگانه ولتاژ پایین با کارایی بالا |

| عنوان انگلیسی مقاله: |

Design and Optimization of Low Voltage High Performance Dual Threshold CMOS Circuits |

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار مقاله | 1998 |

| تعداد صفحات مقاله انگلیسی | 6صفحه با فرمت pdf |

| رشته های مرتبط با این مقاله | مهندسی برق |

| گرایش های مرتبط با این مقاله | مدارهای مجتمع الکترونیک، مهندسی الکترونیک و مهندسی کنترل |

| مجله مربوطه |

سی و پنجمین کنفرانس سالانه اتوماسیون طراحی – 35th annual Design Automation Conference |

| دانشگاه تهیه کننده | دانشکده برق و کامپیوتر، دانشگاه پوردو، ایالات متحدده آمریکا |

| لینک مقاله در سایت مرجع | لینک این مقاله در سایت ACM |

| نشریه | ACM |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش و فونت 14 B Nazanin | 18صفحه |

| ترجمه عناوین تصاویر و جداول | ترجمه شده است |

| ترجمه متون داخل تصاویر | ترجمه نشده است |

| ترجمه متون داخل جداول | ترجمه نشده است |

| درج تصاویر در فایل ترجمه | درج شده است |

| درج جداول در فایل ترجمه | درج شده است |

| درج فرمولها و محاسبات در فایل ترجمه به صورت عکس | درج شده است |

| منابع داخل متن | به صورت عدد درج شده است |

- فهرست مطالب:

چکیده

1. مقدمه

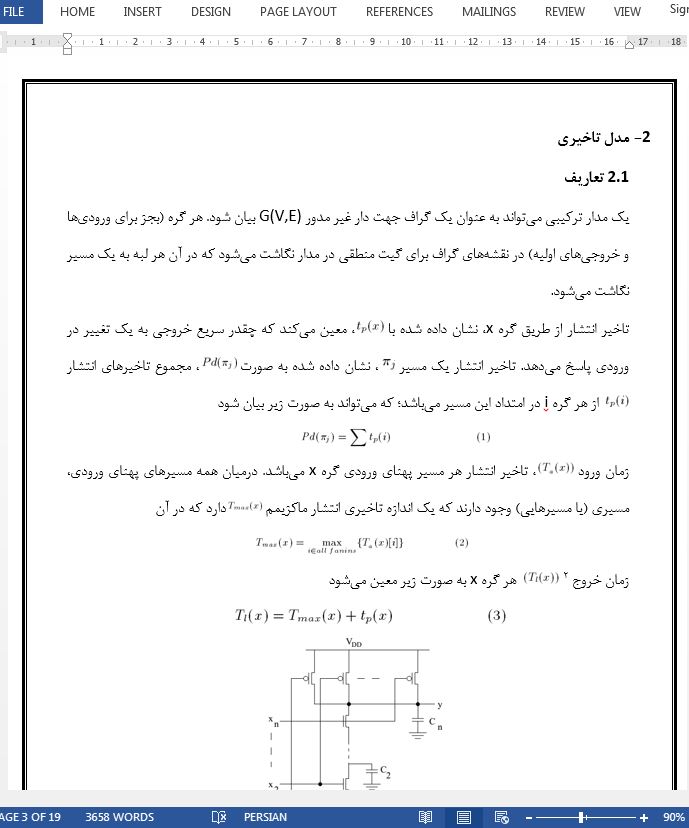

2. مدل تاخیری

2.1 تعاریف

2.2 مدل تاخیری Elmore

3-تخمین توان نشت آماده به کار

4-الگوریتم

5-اجرا و نتایج

6-نتیجه گیری

- بخشی از ترجمه:

6- نتیجه گیری در این مقاله، ما روشی را برای طراحی و بهینه سازی مدارهای CMOS ولتاژ آستانه دوگانه ولتاژ پایین ارائه میدهیم. برای کاهش توان نشت تحت قیدهای عملکردی، با شروع از یک مدار ولتاژ آستانه پایین منفرد، یک الگوریتم اکتشافی برای انتخاب و تعیین یک ولتاژ استانه بالای بهینه پیشنهاد شده است. برای تخمین توان نشت دقیق، یک مدل جریان نشت آماده به کار که تصدیق شده است توسط شبیه سازی HSPICE استفاده میشود. نتایج برای مدارهای مبنای ISCAS نشان میدهند که توان نشت میتواند با بیش از 50% تحت قیدهای عملکردی کاهش یابد. ولتاژهای آستانه بالای بهینه بین و میباشند با توجه به انکه ولتاژ آستانه است. اتلاف توان فعال کل میتواند با استفاده از تکنیک طراحی ولتاژ آستانه دوگانه کاهش یابد. صرفه جویی توان کل میتواند حدود 13% برای برخی مدارها در فرکانس 100MHz باشد.

- بخشی از مقاله انگلیسی:

6 Conclusions

In this paper we present a method to design and optimize low voltage dual-Vth CMOS circuits. In order to reduce leakage power under performance constraints, starting with a single low Vth circuit, a heuristic algorithm for selecting and assigning an optimal high threshold voltage is proposed. For accurate leakage power estimation, a standby leakage current model which has been verified by HSPICE simulation is used. Results for ISCAS benchmark circuits show that the leakage power can be reduced by more than 50% under performance constraints. The optimal high threshold voltages are between 0.3Vdd and 0.4vddr given that the low threshold voltage is 0.2Vdd. The total active power dissipation can also be reduced using dual-Vth design technique. The total power saving can be about 13% for some circuit at 1OOMHz frequency.

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

طراحی و بهینه سازی مدارهای CMOS آستانه دوگانه ولتاژ پایین با کارایی بالا |

| عنوان انگلیسی مقاله: |

Design and Optimization of Low Voltage High Performance Dual Threshold CMOS Circuits |

|

|