گروه آموزشی ترجمه فا اقدام به ارائه ترجمه مقاله با موضوع ” تشخیص تله رابط به عنوان مسئول هیستریتز در ترانزیستورهای نازک ” در قالب فایل ورد نموده است که شما عزیزان میتوانید پس از دانلود رایگان مقاله انگلیسی و نیز مطالعه نمونه ترجمه و سایر مشخصات، ترجمه را خریداری نمایید.

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

توصیف دینامیک فاصله کوچک ( تله) رابط در ترانزیستور های آلی نازک لایه، به عنوان مسئول ایجاد هیسترزیس |

| عنوان انگلیسی مقاله: |

Characterization of interface trap dynamics responsible for hysteresis in organic thin-film transistors |

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار | 2015 |

| تعداد صفحات مقاله انگلیسی | 5 صفحه با فرمت pdf |

| رشته های مرتبط با این مقاله | مهندسی برق |

| گرایش های مرتبط با این مقاله | الکترونیک قدرت وماشینهای الکتریکی ، مهندسی الکترونیک و برق قدرت |

| مجله | الکترونیک ارگانیک – Organic Electronics |

| دانشگاه | گروه مهندسی الکترونیک و کامپیوتر، دانشگاه علم و صنعت هنگ کنگ |

| کلمات کلیدی | ترانزیستورهای فیلم نازک آلی، هیسترزیس، دامنه رابط، مشخصه |

| شناسه شاپا یا ISSN | ISSN 2015.09.011 |

| رفرنس | دارد |

| لینک مقاله در سایت مرجع | لینک این مقاله در نشریه Elsevier |

| نشریه | الزویر – Elsevier |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش و فونت 14 B Nazanin | 12 صفحه |

| ترجمه عناوین تصاویر | ترجمه شده است |

| ترجمه متون داخل تصاویر | ترجمه نشده است |

| درج تصاویر در فایل ترجمه | درج شده است |

| درج جداول در فایل ترجمه | ندارد |

| درج فرمولها و محاسبات در فایل ترجمه به صورت عکس | درج شده است |

- فهرست مطالب:

چکیده

1.مقدمه

2. ساختار دستگاه و اندازه گیری های جامع گیت به صورت دو سویه

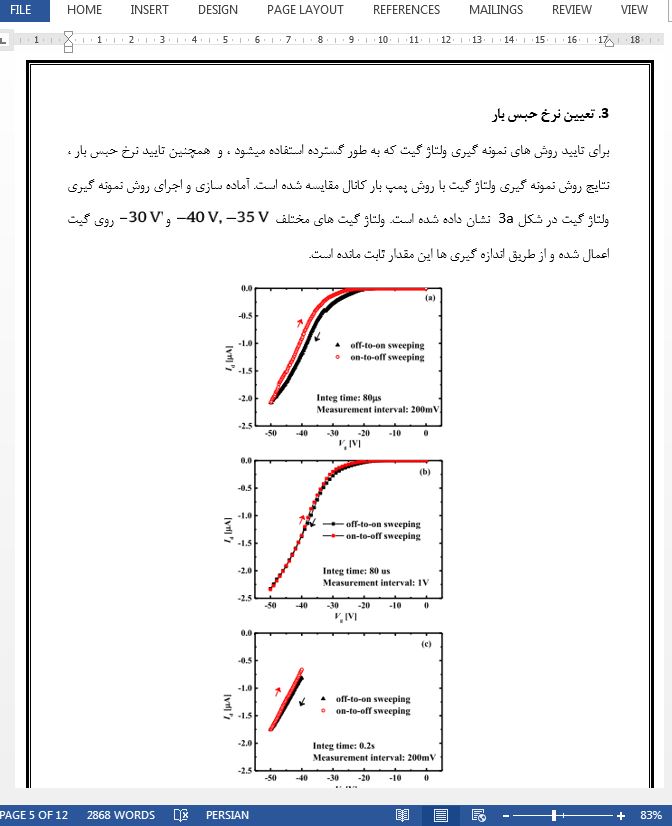

3. تعیین نرخ حبس بار

4. تعیین نرخ آزاد سازی بار

5. نتایج

- بخشی از ترجمه:

5. نتایج

در این مقاله ، روش نمونه گیری ولتاژ گیت برای استخراج نرخ های حبس و آزاد سازی الکترون ها مورد استفاده قرار گرفت. روند رها سازی در طول اندازه گیری ها به طور کامل توضیح داده شده و معادلات مربوطه به دست آمده است. نرخ حبس تقریبا 30 s تخمین زده شد در حالی که نرخ رها سازی حدود 0.5 s تخمین زده شد. برای تایید اعتبار روش استفاده شده ، روش پمپ شارژ کانال نیز استفاده شده است. به این علت که در روند های حبس و آزاد سازی ، تراکم کلی تله ها در هر دو روش تقریبا با هم مطابقت داشت ، و هر دو مقداری نزدیک به 3.2 *10^13 cm^-2 را نتیجه دادند ، صحت تکنیک ها تایید میشود.

- بخشی از مقاله انگلیسی:

5. Conclusion

In this paper, the gate-voltage sampling method is applied to extract both the trapping and detrapping rates. The detrapping process during the measurement is explained and the relevant equations are derived. The estimated trapping rate is around 30 s while the detrapping rate is about 0.5 s. To verify the validity of the technique, the channel charge pumping method is used. Since in the trapping and detrapping process the total trap densities measured using both methods are consistent with each other, giving a value close to 3.2 *10^13 cm^-2 , the accuracy of the technique is confirmed.

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

تشخیص پویایی تله رابط به عنوان مسئول هیستریتز در ترانزیستورهای نازک لایه |

| عنوان انگلیسی مقاله: |

Characterization of interface trap dynamics responsible for hysteresis in organic thin-film transistors |

|

|