دانلود مقاله ترجمه شده مدار ترتیبی با مکمل منطق ترانزیستور عبور – مجله IEEE

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

مدارهای ترتیبی بی دررو کم توان با منطق مکمل ترانزیستور عبوری |

| عنوان انگلیسی مقاله: |

Low-Power Adiabatic Sequential Circuits with Complementary Pass-Transistor Logic |

|

|

| مشخصات مقاله انگلیسی (PDF) | |

| سال انتشار | ۲۰۱۰ |

| تعداد صفحات مقاله انگلیسی | ۴ صفحه با فرمت pdf |

| رشته های مرتبط با این مقاله | مهندسی برق |

| گرایش های مرتبط با این مقاله | مهندسی الکترونیک و مدارهای مجتمع الکترونیک |

| مجله | چهل و هشتمین سمپزیوم مدارات و سیستم ها |

| دانشگاه | دانشکده علوم و فناوری اطلاعات Ningbo، چین |

| رفرنس | دارد |

| لینک مقاله در سایت مرجع | لینک این مقاله در سایت IEEE |

| نشریه | IEEE |

| مشخصات و وضعیت ترجمه فارسی این مقاله (Word) | |

| تعداد صفحات ترجمه تایپ شده با فرمت ورد با قابلیت ویرایش و فونت ۱۴ B Nazanin | ۱۰صفحه |

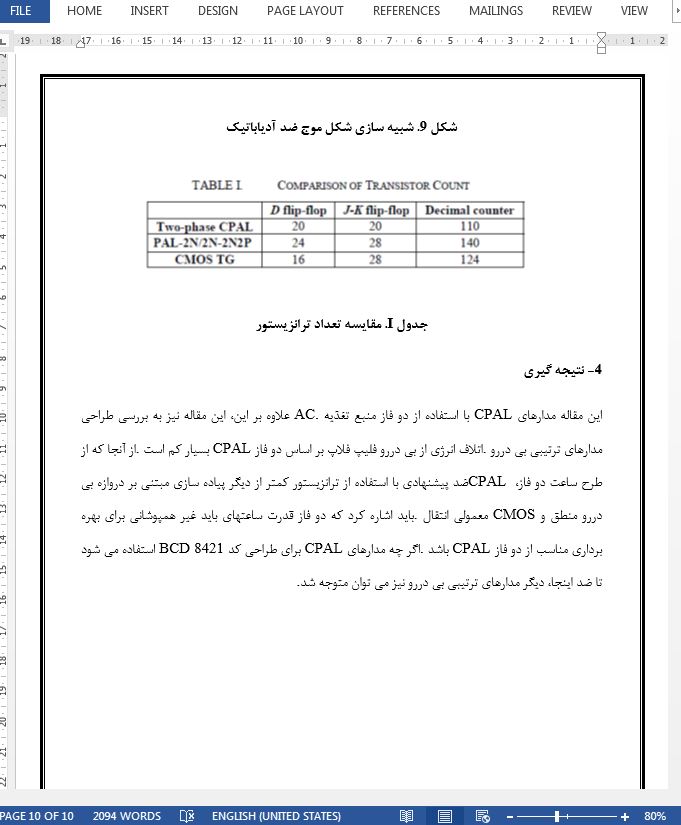

| ترجمه عناوین تصاویر و جداول | ترجمه شده است |

| ترجمه متون داخل تصاویر | ترجمه نشده است |

| ترجمه متون داخل جداول | ترجمه نشده است |

| درج تصاویر در فایل ترجمه | درج شده است |

| درج جداول در فایل ترجمه | درج شده است |

| درج فرمولها و محاسبات در فایل ترجمه به صورت عکس | درج شده است |

- فهرست مطالب:

چکیده

مقدمه

۲-CPAL دو فاز

۳-فلیپ فلاپ های بی دررو و مدارهای بخشی

۴- نتیجه گیری

- بخشی از ترجمه:

۴- نتیجه گیری

این مقاله مدارهای CPAL با استفاده از دو فاز منبع تغذیه AC. علاوه بر این، این مقاله نیز به بررسی طراحی مدارهای ترتیبی بی دررو. اتلاف انرژی از بی دررو فلیپ فلاپ بر اساس دو فاز CPAL بسیار کم است. از آنجا که از طرح ساعت دو فاز، CPAL ضد پیشنهادی با استفاده از ترانزیستور کمتر از دیگر پیاده سازی مبتنی بر دروازه بی دررو منطق و CMOS معمولی انتقال. باید اشاره کرد که دو فاز قدرت ساعتهای باید غیر همپوشانی برای بهره برداری مناسب از دو فاز CPAL باشد. اگر چه مدارهای CPAL برای طراحی کد ۸۴۲۱ BCD استفاده می شود تا ضد اینجا، دیگر مدارهای ترتیبی بی دررو نیز می توان متوجه شد.

- بخشی از مقاله انگلیسی:

IV. CONCLUSIONS This paper presents CPAL circuits using two-phase AC power supply. Moreover, this paper also explores the design of adiabatic sequential circuits. The energy dissipation of the adiabatic flip-flops based on the two-phase CPAL is very low. Because of two-phase clock scheme, the proposed CPAL counter uses fewer transistors than the other adiabatic logic and conventional CMOS transmission gate-based implementations. It should be pointed that the two-phase power-clocks must be non-overlap for proper operation of two-phase CPAL. Although the CPAL circuits are used for the design of an 8421 BCD code up-counter here, the other adiabatic sequential circuits can be also realized.

|

تصویری از مقاله ترجمه و تایپ شده در نرم افزار ورد |

|

|

| دانلود رایگان مقاله انگلیسی + خرید ترجمه فارسی

|

|

| عنوان فارسی مقاله: |

مدار ترتیبی بی دررو کم توان با منطق مکمل ترانزیستور عبوری |

| عنوان انگلیسی مقاله: |

Low-Power Adiabatic Sequential Circuits with Complementary Pass-Transistor Logic |

|

|